Advantages

- 半導体デバイス製造に用いるエッチングプラズマから得た電荷を電源として、デバイス製造中に小規模な回路を駆動するという新しい考え方を提案

- 物理複製困難関数(PUF)での利用を研究中。デバイスの製造中にPUFを書き込むことで、分離不可能かつ信頼性の高いPUFとなる

- CMOSプロセスにてチップを製造し技術を実証済み。エッチングプラズマを電源として、十分なエントロピーを持つPUFの生成に成功

- デバイスの品質確認や、問題検知時の校正など、他の用途も提案を歓迎

Background and Technology

大阪大学情報科学研究科の三浦典之教授は、半導体デバイスの製造プロセスに用いるエッチングプラズマを未開拓の電力源として活用する新技術を提案する。

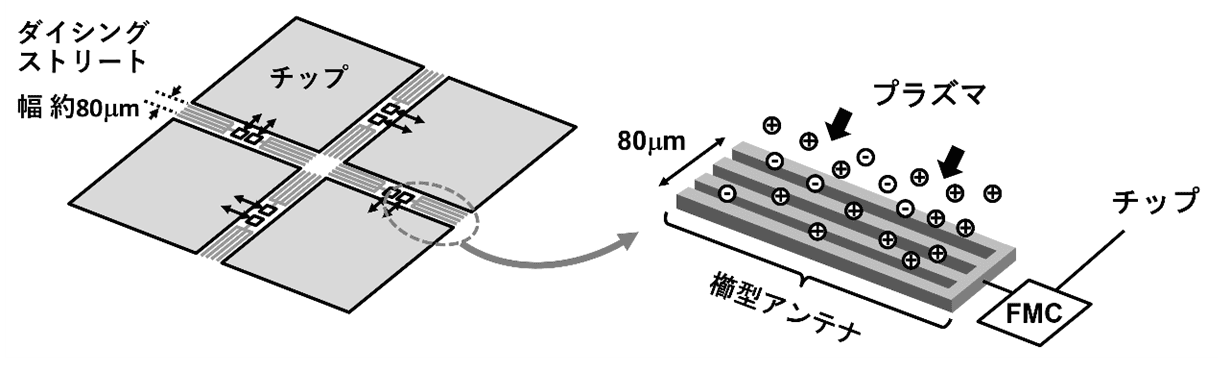

本技術のコアは、半導体ウェハ上のダイシングストリートに予め形成した「アンテナ」を使い、エッチングプラズマを収集することだ(図1)。アンテナが集めたプラズマ電荷が、ダイシングストリートや半導体チップ内に配置した回路を駆動する。三浦教授らはこうした回路を、デバイスの製造中に駆動するという意味を込めて、「胎動回路 Fetal Movement Circuit」と呼ぶ。

図1 胎動回路の概念図

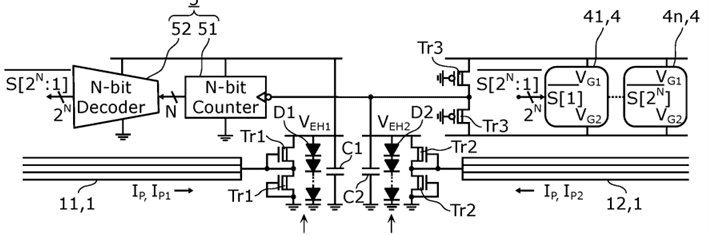

胎動回路は、様々な用途が考えられる。三浦教授らは、胎動回路の一例として、物理複製困難関数(PUF)を考案し、研究や実証を進めている。考案したPUFは、プラズマ収集アンテナ、昇圧回路、PUFの本体であるトランジスタ群と、PUF生成のための駆動回路から成る(図2)。トランジスタ群(図中S[1]からS[2N]まで)は、並列に接続された2つのトランジスタを1組とするトランジスタペアの集まりである。まず、アンテナが収集したプラズマ電荷をもとにした電源電圧が、駆動回路(図中左のカウンターとデコーダー)を通して、このトランジスタ群に印加される。すると、トランジスタペア毎に、耐電圧が低い(つまり、ゲート酸化膜が弱い)トランジスタが先に破壊され、これが全てのトランジスタペアで発生する。ペアのどちらが破壊されるかは完全にランダムであり、再現もできない。こうしてこの破壊から生き残ったトランジスタ群がPUFとなる。チップを使用する際にこのPUFの破壊パターンを読み出すことで、PUFレスポンスが得られる。

図2 PUFを生成する胎動回路

本技術の特徴は、2つある。PUFを物理的にデバイスから分離することができないという高いセキュリティと、従来捨てられていたエネルギー源を用いるコストメリットだ。本技術のPUFは半導体デバイスの製造と並行して生成されるため、デバイスの中に組み込まれてしまい、分離するにはデバイスを破壊することになる。従来のPUFではデバイスと分離できてしまうものもある中で、本技術のPUFはセキュリティをより担保すると考えられる。また、本技術のPUFの作成には外部の電源を必要としないため、デバイス製造装置のハードウェア的な改修のコストを低くでき、製造プロセスの変更も抑えることができる。また、エネルギー面でも従来のプロセスに付加するものではなく、コスト的な増加はほとんどない。

なお、胎動回路技術の応用はPUFにかぎらない。例えば、半導体製造プロセスにおけるエッチングプラズマ量のモニタリングや、製造中チップの品質検査・検査を反映したチップの校正といった品質管理機能、上記以外の原理からなるPUFの作成など、さまざまな用途が考えられる。

Data

三浦教授らは、本記事で説明したPUFの動作実証を進めている(文献1参考)。

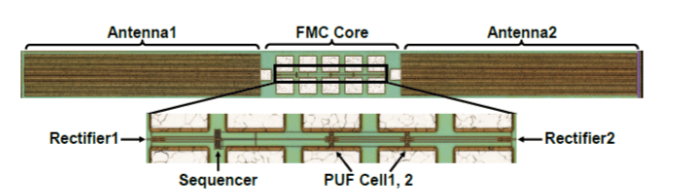

- 技術実証のために、180nm CMOSのプロセスによりテストチップを製造した。製造した回路(図3)は、アンテナと制御回路、PUF cell(トランジスタのペア)と、電圧測定端子(図中の白色部)からなる。ひとつのテストチップ上にPUF cellを230個配置した。

- 上記回路をテストチップの製造する過程で、期待通り、エッチングプラズマをエネルギー源として胎動回路が駆動し、PUFが作成された。テストチップ製造後にPUF cell毎に内部のトランジスタの電流を測定したところ、全てのcellにおいてペアのうち片方が破壊されていたことが確認できた。

- 全てのPUF cellの電流値を測定し、電流値の高低をもとに2値のPUFレスポンスを作成した。このレスポンスのエントロピーはおよそ0.5であり、PUFとして十分に実用的な複雑性がある。

図3 作成したPUF生成回路の写真

Expectations

本技術を用いたPUFや半導体デバイスの開発に関心のある企業とのコラボレーションを提案します。貴社が開発する半導体デバイスのセキュリティ向上として、本技術のPUFをぜひご活用ください。また、PUF以外に次のような用途も想定されます。

- 製造途中におけるデバイスの品質テスト。テスト用回路を胎動回路によって駆動する。テストに係る費用や時間のコストを削減する可能性がある。

- チップの事前構成。上記のテスト結果をもとに、良好な回路動作条件を算出し、その条件に必要なパラメータを不揮発性メモリへ、製造中に書き込む。

本技術を貴社に移転するに当たっては、貴社主導での取り組みをお願いいたします。大学からは、貴社の開発に対し、以下のようなお手伝いをご相談できます。

・ご質問への対応(秘密情報を除く)

・先生とのご面談による詳細説明

・NDA締結下での情報交換

・共同研究

・特許ライセンス

Publications

- 文献1:本技術を説明する、三浦先生らの発表資料

A Fetal-Movement Circuit Harvesting High-Energy Plasma During Fabrication, Concept, and Its Application to Self-Programming PUF

https://ieeexplore.ieee.org/document/10247264

Patents

- PCT出願中 WO/2024/157600

以下のフォームからお問い合わせください