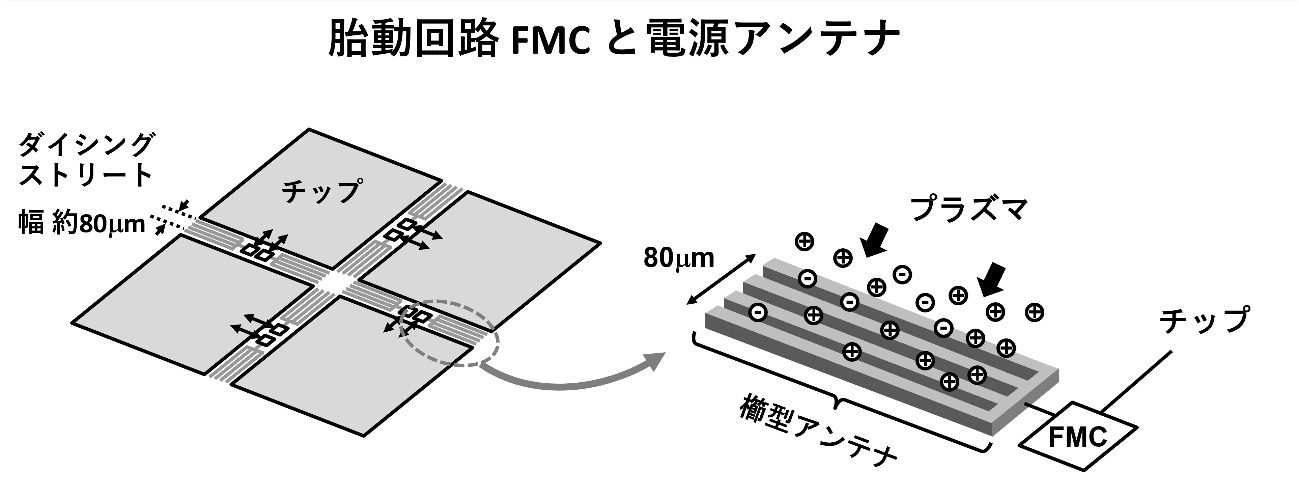

~ダイシングストリート内のアンテナでプラズマ電流を収集し、酸化物破壊PUFや品質評価回路を製造・駆動~

Advantages

- 半導体製造中に生じるエッチングプラズマから電力を取得して動作する電子回路

- 半導体の品質検査回路や物理複製困難関数(PUF)回路、その他半導体ウェハ上の付属回路を外付け電源なしで駆動

- 180nm標準CMOSで製造したテストチップによる予備評価でPUFセルの動作を実証済み

Background and Technology

半導体製造プロセスにおけるエッチングプラズマはトランジスタのゲート酸化膜を破壊して劣化させるほど高エネルギーである。大阪大学情報科学研究科の三浦典之教授は、このプラズマを未開拓の電力源として活用する半導体回路を提案する。工程上、半導体チップの間に挿入する必要があるダイシングストリート内に形成した櫛形のアンテナパターンを使い、エッチングプラズマを収集することで得た電流を電源として、ダイシングストリート内や半導体チップ内に配置した回路、以下「胎動回路」という、を駆動する技術である。例えば、半導体製造プロセスにおけるエッチングプラズマ量のモニタリングや、製造中チップの品質を判定したりチップの校正を行う品質管理機能、物理複製困難関数(PUF)の書き込みなど、さまざまな用途が考えられる。本技術を使えば、シリコン面積を胎動回路用に余分に確保する必要がなく、胎動回路を駆動するための電源を外部から別付けする必要もなく、従来の半導体製造プロセスからほとんど変わりなくプロセス中の特殊な回路を組み込むことができる。

現在大阪大学で最も研究が進んでいるのが、胎動回路を使った物理複製困難関数(PUF)の書き込み技術である。具体的には、高電圧によってチップ内のトランジスタをランダムに破壊することでPUFの認証パターンを生成する技術において、ダイシングストリートに構築されたプラズマ収集アンテナと電源回路からトランジスタ破壊用の高電圧を供給する手法である。この方法で生成される認証パターンは物理的に書き込まれるため、読み取り時の不安定性がほとんどなく、正確性の高いPUFになると期待される。大阪大学ではすでに180nm標準CMOSで製造したテストチップによる予備評価で、PUFセルの動作を実証済みである。

Expectation

本技術を用いた技術や製品開発に関心のある企業とのコラボレーションを提案します。大学ではすでに半導体素子に胎動回路を書き込み、駆動することを確認しています。本技術を企業の技術や製品に移転するに当たっては、企業が主導で取り組んでいただくことを期待します。しかし、大学から、企業が技術開発を行う中で必要な科学的知見を提供したり、開発方針をご相談するなど様々なお手伝いが可能です。また、最終的には、大学が保有する特許をライセンスすることで事業の排他性を確保することができます。

Publication

・Kotaro Naruse, Takayuki Ueda, Jun Shiomi, Yoshihiro Midoh, and Noriyuki Miura, “A Self-Programming PUF Harvesting the High-Energy Plasma During Fabrication,” International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, pp. 218-219, Feb. 2023.

Patent

- 特許出願中

以下のフォームからお問い合わせください