Advantages

- 大阪大学 兼本先生らが、低ドロップアウトレギュレータの新回路を開発

- 高い電圧周波数(数kHz以上)でのノイズ除去性能(PSRR)に優れる

- 世界最小レベルの超低消費電力を、高機能と同時に実現

- チップにてPoCを検証中

- LSIメーカーとの製品化や、IoT/ウェアラブルデバイスメーカーとの共同開発を歓迎

Background and Technology

大阪大学工学研究科の兼本大輔准教授らは、ユーザーに負担が少ないウェアラブルな脳波計を研究する中で、超低消費電力と高性能を両立する低ドロップアウトレギュレータ(LDO)技術を開発しました。

彼らは、自身のウェアラブルかつワイヤレスな脳波計に対し、非常に厳しい低電力化を求め、その中で削減対象としてLDOに注目しました。LDOは、バッテリーやDC-DCコンバータなどが生成する直流電圧(入力電圧)を、下流の素子が使うための低い直流電圧(出力電圧)に変換する素子です。LDOにはさらに、入力電圧が持つ変動成分「リップル」を除去する機能も求められ、このリップル抑制の能力はPSRR(Power Supply Rejection Ratio)と呼ばれます。

兼本先生らは、LDOに対して、高いリップル抑制能力も求めました。脳波は微弱な信号なのでできるだけきれいな電源信号が必要だからです。典型的なLDOは低周波数(直流から数kHz)のリップル除去能力は高いですが、高い周波数(数kHz以上)の能力は乏しいと言われています。この問題(高周波数でPSRRが悪い)を解決するために、「LDOの多段化」に代表されるいくつかの方法が提案されていますが、それらは消費電力を大きくする方向に働きます。兼本先生らは、従来の常識を覆す、画期的なLDOの開発を目指し研究を続けました。

先生方が到達した高性能LDOは、彼らが独自開発した「補助増幅器」の回路で構成されており、高い周波数帯のPSRRを10 dB以上も改善することに成功しました。しかも、消費電力は、マイクロアンペアを下回る極小です。これは市販されているLDOチップの中でも最小品と同等かそれより低い値です。

技術的な詳細は以下の通りです。

- PSRRの改善にはLDO回路における一巡伝達関数の利得を高めることが重要。これは高帯域差動増幅器を使用することで幅広い周波数で高い利得を実現して得られるが、消費電力を増加させてしまう。

- 独自に開発した、低消費電流と低電圧動作を特徴とする補助増幅器を、シンプルな構成のLDOに結合することで、高い周波数域での良PSRRを実現した。

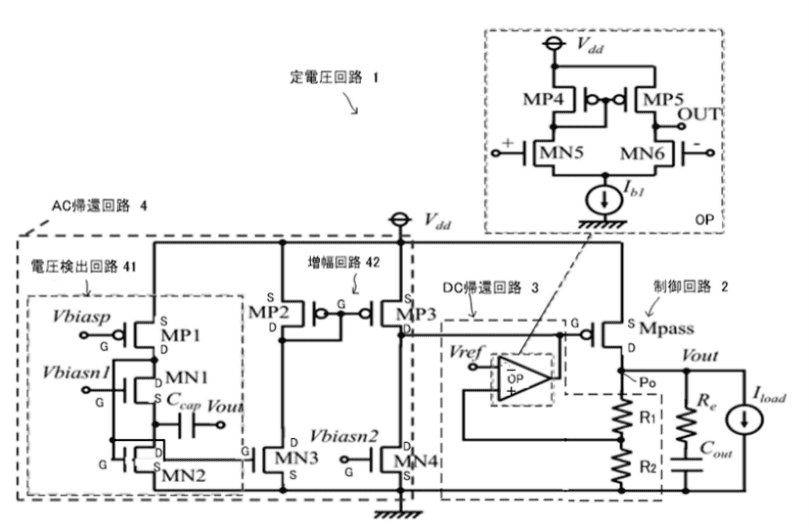

- この補助増幅器は、Flipped Voltage Follower(FVF)フィルタと、FVFのゲインを上げるためのソース接地増幅器を組み合わせた独自回路「FVF-based PSRR-enhanced circuit(FBPEC)」。(図1参照)

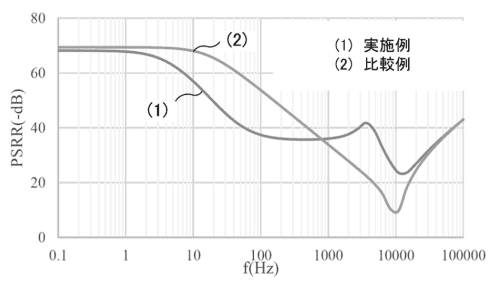

- 低周波数帯が得意な一般のLDOと、高周波数帯で優れた応答特性を持つFBPECとを組み合わせることで、全体として広い帯域での優れたPSRRを実現。(図2参照)

図1 本技術の回路構成

図2 PSRRの比較。比較例は図1の回路から、本技術の回路FBPECを除いたもの。

Expectations

- この技術は、シミュレーションレベルでは動作を確認しています。24年春現在、試作チップを作成し、評価実験中です。

- チップメーカー様へ、新規のLDOチップとして製品化をご提案します。

- IoTやウェアラブルデバイスなどの低消費電力化を求める企業様との共同開発をご提案します。

<チップメーカー様へ>

大阪大学では本技術を採用したLDOレギュレータの製品化に関心をお持ちの企業を探しています。現在、実機での動作実証を行っておりますが、ぜひ貴社の製品アーキテクチャに導入いただき、貴社製品の優位性向上にお役立てできますと幸いです。製品開発において必要な情報(回路や部品選定など)を秘密保持契約のもとで提供できます。また、特許ライセンスを大阪大学から受けることで、独自性を担保できます。

<IoT製品・システムメーカー様へ>

大阪大学では本技術の技術的優位性についてLDOレギュレータのユーザーであるIoT 企業様との意見交換を期待しています。IoT製品のメーカー様より省電力化へのニーズ情報をいただけましたら、チップメーカー様へ一緒に製品化を提案しませんか?ぜひ貴社のご意見を伺う機会をいただけますと幸いです。

本技術は、ワイヤレスイヤホン、カメラ、スマートグラスなどのウェアラブルデバイス、ヘルスケアモニタリング用の医療機器、工業・農業・インフラなどで用いるIoTエッジデバイスで、これまでにない低コスト化の推進をお手伝いします。

Publications

- FVFを応用したPSRR帯域拡張回路を搭載した脳波計測ウェアラブルデバイス向け低消費LDO; デザインガイア2021

- “Low quiescent current LDO with FVF-based PSRR enhanced circuit for EEG recording wearable devices”; Kenji Mii et al 2024 Jpn. J. Appl. Phys. 63 03SP33

Patents

PCT/JP2022/037552

Researchers

大阪大学 大学院工学研究科

兼本 大輔 准教授

以下のフォームからお問い合わせください